# Unit 5 – Combinational Circuits

# **BASIC CIRCUITS**

#### MULTIPLEXERS (MUXS)

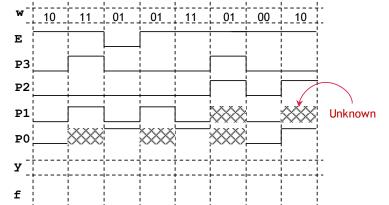

- This logic circuit selects one of many input signals and forwards the selected input to the output line.

- Boolean equations for MUX2-to-1, MUX4-to-1, MUX8-to-1:

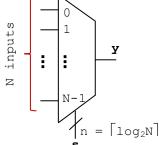

- Normally, a multiplexer has  $N = 2^n$  inputs, one output, and a selector with *n* bits.

- But, if a multiplexer has N inputs, where N is not a power of 2, the number of bits of the selector is given by:  $[log_2N]$ .

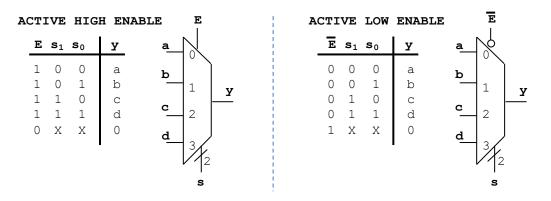

#### **MULTIPLEXERS WITH ENABLE**

- An enable input provides us with an extra level of control. If the multiplexer is enabled, the circuit just works. If the

multiplexer is not enabled, no input is allowed into the output, and the multiplexer output becomes '0' (if the output is activehigh) or '1' (if the output if active-low).

- The enable input can be either active-high or active-low:

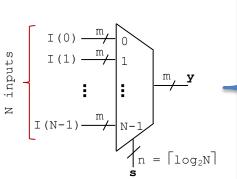

#### **BUS MULTIPLEXERS**

- Usually we want input signals to contain more than one bit.

- In the figure, each input signal contains 'm' bits.

- This 'bus multiplexer' can be built by 'm' multiplexers, each taking care of only one bit for all the inputs.

- We have 'N' inputs and therefore the selector has n = [log<sub>2</sub>N] bits.

- Note that the selector is the same for all the multiplexers.

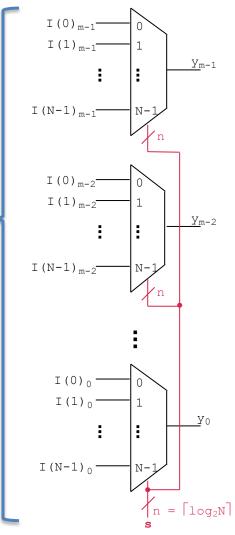

#### LOGIC CIRCUITS WITH MUXs

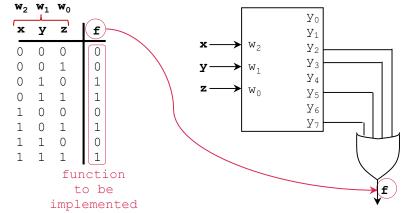

- Multiplexers can be used to implement Boolean Functions. The selector can be thought as the input variables, the input bits

are fixed values that are passed onto the output according to the selector.

- This multiplexor with fixed inputs implements a logic function. The functionality of this circuit is similar to that of a Look-Up Table (LUT), which is a ROM-like circuit whose values are obtained by addressing them. FPGAs implement Boolean functions using LUTs. In the example, a 3-to-1 LUT is an LUT with 3 inputs, i.e., it contains 2<sup>3</sup> = 8 addresses.

- Note that for a *n*-variable function, we need a MUX 2<sup>*n*</sup>-to-1 with fixed inputs.

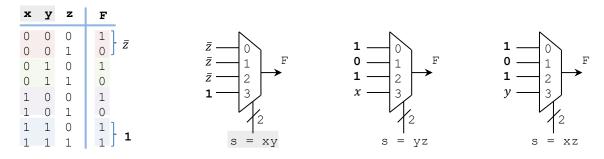

- However, it is possible to use a MUX  $2^{n-1}$ -to-1. This might require extra NOT gates and non-fixed inputs.  $\checkmark F(x, y, z) = \sum (m_0, m_2, m_4, m_6, m_7).$

✓  $F(x, y, z) = \sum (m_0, m_1, m_3, m_5, m_7).$

| х | У | z | F |

|---|---|---|---|

| 0 | 0 | 0 | 1 |

| 0 | 0 | 1 | 1 |

| 0 | 1 | 0 | 0 |

| 0 | 1 | 1 | 1 |

| 1 | 0 | 0 | 0 |

| 1 | 0 | 1 | 1 |

| 1 | 1 | 0 | 0 |

| 1 | 1 | 1 | 1 |

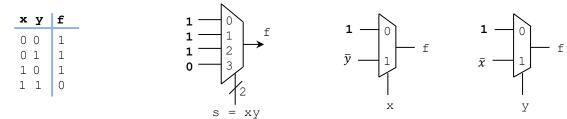

$\checkmark \quad F(x, y) = \sum (m_0, m_1, m_2)$

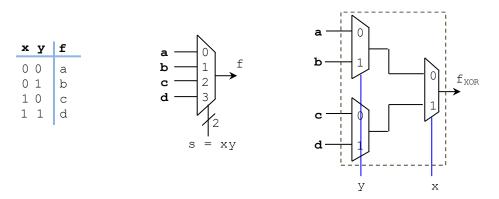

This process of using multiplexors to implement functions can be performed in a systematic fashion using **Shannon's expansion theorem**. As we will see later for LUTs, this has an important application in the implementation of Boolean functions on FPGAs.

#### Example:

Implement a MUX 4-to-1 using MUXes 2to-1.

#### SHANNON'S EXPANSION

- This is useful to express a Boolean function in terms of multiplexers

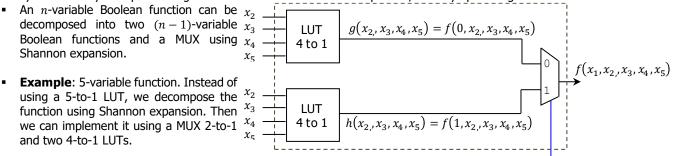

- An *n*-variable Boolean function can be decomposed into two (n 1)-variable Boolean functions:

$$f(x_1, x_2, \dots, x_n) = \overline{x_1} f(0, x_2, \dots, x_n) + x_1 f(1, x_2, \dots, x_n)$$

- In the equation, we use the variable  $x_1$  to decompose, but we can use any variable  $x_i$ , i = 1:n. For example, using  $x_n$ :  $f(x_1, x_2, ..., x_n) = \overline{x_n} f(x_1, x_2, ..., 0) + x_n f(x_1, x_2, ..., 1)$

- A short-hand notation of the Shannon expansion is as follows:

$$f = \overline{x_i} f_{\overline{x_i}} + x_i f_{x_i}$$

$\chi_i$

Note that we can implement f using a 2-to-1 MUX, as the equation resembles that of the MUX.

Examples:

$$f = x_1 x_2 + \overline{x_1} x_3 + x_2 x_3$$

$$f = \overline{x_1} f(0, x_2, x_3) + x_1 f(1, x_2, x_3) = \overline{x_1} (x_3 + x_2 x_3) + x_1 (x_2 + x_2 x_3)$$

We can further apply Shannon expansion to two variable functions:  $f = \overline{x_1}g(x_2, x_3) + x_1h(x_2, x_3)$   $g(x_2, x_3) = \overline{x_2}g(0, x_3) + x_2g(1, x_3) = \overline{x_2}(x_3) + x_2(x_3)$  $h(x_2, x_3) = \overline{x_2}h(0, x_3) + x_2h(1, x_3) = \overline{x_2}(0) + x_2(1)$

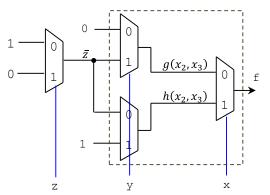

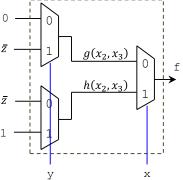

$\checkmark f = \bar{z}y + \bar{z}x + xyz$  $f = \bar{x}f(0, y, z) + xf(1, y, z) = \bar{x}(\bar{z}y) + x(\bar{z}y + \bar{z} + yz)$

$$\begin{split} f &= \bar{x}g(y,z) + xh(y,z) \\ g(y,z) &= \bar{z}y = \bar{y}g(0,z) + yg(1,z) = \bar{y}(0) + y(\bar{z}) \\ h(y,z) &= \bar{z}y + \bar{z} + yz = \bar{y}h(0,z) + yh(1,z) = \bar{y}(\bar{z}) + y(1) \end{split}$$

We can implement  $\bar{z}$  using MUXs:

$p(z) = \bar{z} = \bar{z}p(0) + zp(1) = \bar{z}(1) + z(0)$

Finally, we implement the function f with only 2-to-1 multiplexors:

4

# ELECTRICAL AND COMPUTER ENGINEERING DEPARTMENT, OAKLAND UNIVERSITY ECE-2700: Digital Logic Design

Fall 2024

#### DEMULTIPLEXERS

A demultiplexer performs the opposite operation of the multiplexers.

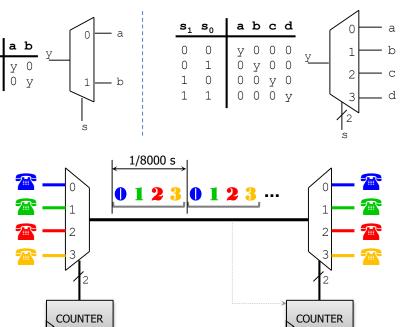

#### Digital Telephony: (4 KHz bandwidth)

**Application:** Time Division Multiplexing (TDM)

- 8000 samples per second, 8 bits per sample. This requires 64000 bits per second.

- In the figure, there are 4 telephone lines (4 signals). To take advantage of the communication channel, only one signal is transmitted at a time. We can do this since we are only required to transmit samples of a particular signal at the rate of 8000 samples per second (or 125 us between samples, this is controlled by counters).

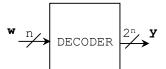

#### DECODERS

- Generally speaking, decoders are circuits that transform the inputs into outputs following a certain rule, provided that the number of outputs is greater than or equal to the number of inputs.

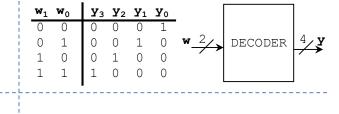

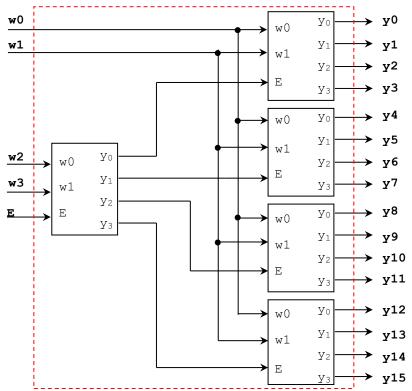

- Here, we discuss standard decoders for which a specific input/output rule exists. These decoders have n inputs and  $2^n$  outputs. We show examples of: a 2-to-4 decoder, 3-to-8 decoder, and a 2-to-4 decoder with enable. The output  $y_i$  is activated when the decimal value of the input w is equal to i.

| <b>w</b> 2 | $\mathbf{w}_1$ | $\mathbf{w}_0$ | <b>Y</b> 7 | <b>Y</b> 6 | <b>Y</b> 5 | <b>Y</b> 4 | <b>Y</b> 3 | <b>Y</b> 2 | <b>y</b> 1 | <b>y</b> 0 |

|------------|----------------|----------------|------------|------------|------------|------------|------------|------------|------------|------------|

| 0          | 0              | 0              | 0          | 0          | 0          | 0          | 0          | 0          | 0          | 1          |

| 0          | 0              | 1              | 0          | 0          | 0          | 0          | 0          | 0          | 1          | 0          |

| 0          | 1              | 0              | 0          | 0          | 0          | 0          | 0          | 1          | 0          | 0          |

| 0          | 1              | 1              | 0          | 0          | 0          | 0          | 1          | 0          | 0          | 0          |

| 1          | 0              | 0              | 0          | 0          | 0          | 1          | 0          | 0          | 0          | 0          |

| 1          | 0              | 1              | 0          | 0          | 1          | 0          | 0          | 0          | 0          | 0          |

| 1          | 1              | 0              | 0          | 1          | 0          | 0          | 0          | 0          | 0          | 0          |

| 1          | 1              | 1              | 1          | 0          | 0          | 0          | 0          | 0          | 0          | 0          |

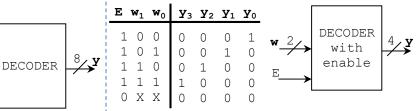

# LOGIC CIRCUITS WITH DECODERS

- Decoders can be used to implement Boolean functions. Note that each output is actually a minterm.

- In the example, minterm 2 is activated when xyz=010, here only y<sub>2</sub> is 1. Also: y<sub>5</sub> is activated when xyz=101, y<sub>7</sub> is activated when xyz=111.

$\mathbf{Y}_0$

$\mathbf{y}_2 \ \mathbf{y}_1$

$\mathbf{E} \mathbf{w}_1$

$\mathbf{w}_0 \mid \mathbf{y}_3$

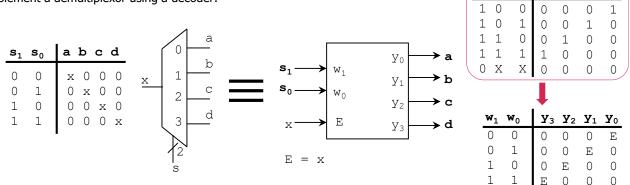

#### IMPLEMENTING DEMULTIPLEXORS WITH DECODERS

By utilizing the enable input of a decoder as our input signal, we can effectively implement a demultiplexor using a decoder:

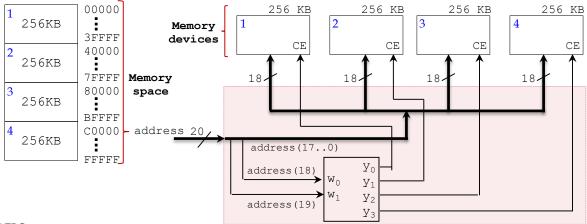

#### Application: Memory Decoding

- A 20-bit address line in a  $\mu$ processor handles up to  $2^{20} = 1 MB$  of addresses, each address containing one-byte of information. We want to connect four 256KB memory chips to the  $\mu$ processor.

- The pink-shaded circuit: i) addresses the memory chips, and ii) enables only one memory chip (via CE: chip enable) when the address falls in the corresponding range. Example: if address = 0x5FFFF,  $\rightarrow$  only memory chip 2 is enabled (CE=1). If address = 0xD0123,  $\rightarrow$  only memory chip 4 is enabled.

#### ENCODERS

- Generally speaking, encoders are circuits that transform the inputs into outputs following a certain rule, provided that the number of outputs is lower than the number of inputs.

- Here, we discuss standard encoders for which a specific input/output rule exists. These encoders have  $2^n$  inputs and n outputs. The operation is exactly the opposite as in the case of the decoder: whenever an input  $w_i$  is activated, then the index *i* appears at the output *y* (in binary form).

- 4 to 2 encoder:

- 8 to 3 encoder:  $y_2 = w_7 + w_6 + w_5 + w_4$   $y_1 = w_7 + w_6 + w_4 + w_3$  $y_0 = w_7 + w_5 + w_3 + w_1$

- Issues:

- ✓ If two or more inputs are activated, the output  $y_{n-1}y_{n-2} ... y_0$  is undefined.

- ✓ If no input is activated, the output  $y_{n-1}y_{n-2} \dots y_0$  is undefined. In this case, the result is ambiguous, as the result would be the same as if only  $w_0 = 1$ , i.e.,  $y_{n-1}y_{n-2} \dots y_0 = 00 \dots 0$ .

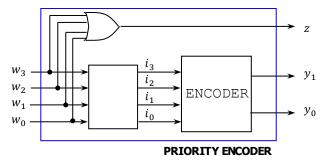

#### PRIORITY ENCODERS

- Standard encoder: we check whether a specific input is activated for the output to have a value.

- What happens when more than one input is activated? A solution is to create an extra output that is activated to indicate than an unexpected condition has occurred.

- An interesting alternative is to create a *priority encoder*: if more than one input is activated, then we only pay attention to the input bit of the highest order. For example if w = 1101, then we only pay attention to w(3) = 1, if w = 0111, we only pay attention to w(2) = 1. This results in the following truth table for a 4-to-2 priority encoder:

- What if no input is activated? Here we run out of output bits in y to represent this case. Thus, we include an extra output z that it is '0' when no input activated, and '1' otherwise.

- For the priority encoder 4 to 2, we can get the Boolean functions directly from the truth table as:  $y_4 = w_0 \overline{w_0} + w_0$

$$y_1 = w_2 w_3 + w_3$$

$$y_0 = \overline{w_3} \overline{w_2} w_1 + w_3$$

$$z = \overline{w_3} \overline{w_2} \overline{w_1} \overline{w_0} = w_3 + w_2 + w_1 + w_0$$

We could simplify  $y_1$  and  $y_0$  (Boolean Theorems, K-maps, or Quine-McCluskey algorithm)

• Alternatively, we can create the following intermediate signals:

| $i_3 = w_3$                                                | $i_3 = 1$ if $w_3 = 1$                         |

|------------------------------------------------------------|------------------------------------------------|

| $i_2 = \overline{w_3}w_2$                                  | $i_2 = 1$ if $w_2 = 1$ , $w_3 = 0$             |

| $i_1 = \overline{w_3}  \overline{w_2} w_1$                 | $i_3 = 1$ if $w_1 = 1, w_2 = w_3 = 0$          |

| $i_0 = \overline{w_3}  \overline{w_2}  \overline{w_1} w_0$ | $i_3 = 1$ if $w_0 = 1$ , $w_1 = w_2 = w_3 = 0$ |

Then, notice that  $i_3 = 1$ ,  $i_2 = 1$ ,  $i_1 = 1$ ,  $i_0 = 1$  are exclusive:

| If                             | $i_3$ | $i_2$ | $i_1$ | i <sub>0</sub> | $y_1$ | $y_0$ | Ζ |

|--------------------------------|-------|-------|-------|----------------|-------|-------|---|

| $w_3 = 1$                      | 1     | 0     | 0     | 0              | 1     | 1     | 1 |

| $w_2 = 1, w_3 = 0$             | 0     | 1     | 0     | 0              | 1     | 0     | 1 |

| $w_1 = 1, w_2 = w_3 = 0$       | 0     | 0     | 1     | 0              | 0     | 1     | 1 |

| $w_0 = 1, w_1 = w_2 = w_3 = 0$ | 0     | 0     | 0     | 1              | 0     | 0     | 1 |

| $w_0 = w_1 = w_2 = w_3 = 0$    | 0     | 0     | 0     | 0              | 0     | 0     | 0 |

Note that the relationship of  $i_3i_2i_1i_0$  to  $y_1y_0$  is that of a binary encoder. If z = 0, then  $y_1y_0 = 00$ .

This procedure can be applied to any priority encoder (e.g.: 8 to 3, 16 to 4).

| w <sub>3</sub> →                                                |      | w <sub>3</sub> | <b>w</b> <sub>2</sub> | $\mathbf{w}_1$ | <b>w</b> <sub>0</sub> | <b>y</b> 1 | <b>Y</b> 0 | z |

|-----------------------------------------------------------------|------|----------------|-----------------------|----------------|-----------------------|------------|------------|---|

| $W_2 \longrightarrow PRIORITY$<br>$W_1 \longrightarrow ENCODER$ | → У1 | 0              | 0                     | 0              | 0                     | 0          | 0          | 0 |

| PRIORITY                                                        | N W  | 1              | Х                     | Х              | х                     | 1          | 1          | 1 |

| $\mathbf{w}_1 \longrightarrow$ ENCODER                          |      |                |                       |                |                       |            |            |   |

|                                                                 | → z  | 0              | 0                     | 1              | х                     | 0<br>0     | 1          | 1 |

| <b>w</b> ₀ →                                                    |      | 0              | 0                     | 0              | 1                     | 0          | 0          | 1 |

|                                                                 |      |                |                       |                |                       | •          |            |   |

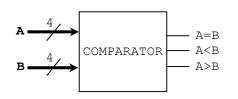

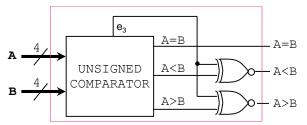

#### COMPARATORS

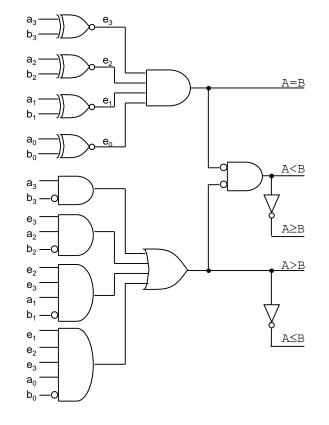

#### **UNSIGNED NUMBERS**

- For  $A = a_3 a_2 a_1 a_0$ ,  $B = b_3 b_2 b_1 b_0$

- ✓ A > B when:  $a_3 = 1, b_3 = 0$ Or:  $a_3 = b_3$  and  $a_2 = 1, b_2 = 0$ Or:  $a_3 = b_3, a_2 = b_2$  and  $a_1 = 1, b_1 = 0$ Or:  $a_3 = b_3, a_2 = b_2, a_1 = b_1$  and  $a_0 = 1, b_0 = 0$

#### SIGNED NUMBERS

- If  $A \ge 0$  and  $B \ge 0$ , we can use the unsigned comparator.

- If A < 0 and B < 0, we can also use the unsigned comparator. Example: 1000<sub>2</sub> < 1001<sub>2</sub> (-8 < -7). The closer the number is to zero, the larger the unsigned value is.</li>

- If one number is positive and the other negative: Example: 1000<sub>2</sub> < 0100<sub>2</sub> (-8 < 4). If we were to use the unsigned comparator, we would get 1000<sub>2</sub> > 0100<sub>2</sub>. So, in this case, we need to invert both the A>B and the A<B bit.</li>

- Rule: For a 4-bit number in 2's complement:

- ✓ If  $a_3 = b_3$ , A and B have the same sign. Then, we do not need to invert any bit.

- ✓ If  $a_3 \neq b_3$ , A and B have a different sign. Then, we need to invert the A>B and A<B bits of the unsigned comparator.

$$e_3 = 1$$

when  $a_3 = b_3$ .  $e_3 = 0$  when  $a_3 \neq b_3$ .

Then it follows that:

$(A < B)_{signed} = \overline{e_3} \oplus (A < B)_{unsigned} = \overline{e_3} \oplus (A < B)_{unsigned}$

$(A > B)_{signed} = \overline{e_3} \oplus (A > B)_{unsigned}$

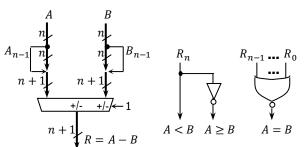

#### ALTERNATIVE APPROACH

- Here, we perform A-B in 2C. If the result is positive (MSB=0), then A ≥ B. If the result is negative (MSB=1), then A < B. We use an 2C adder/subtractor unit to implement this operation (R=A-B):</li>

- $\checkmark\,$  Signed numbers: we need to sign-extend the inputs to consider the worst-case scenario.

- ✓ Unsigned numbers: we need to zero-extend the inputs to convert the values to 2C arithmetic.

- To determine whether *A* is greater than *B*, we use the MSB (*R<sub>n</sub>*):  $R_n = \begin{cases} 1 \to A - B < 0 \\ 0 \end{cases}$

$$n = \{ 0 \to A - B \ge 0 \}$$

• To determine whether A = B, we compare the n + 1 bits of R to 0 (R = A - B). However, note that  $(A - B) \in [-2^n + 1, 2^n - 2]$ . So, the case  $R = -2^n = 10 \dots 0$  will not occur. Thus, we only need to compare the bits  $R_{n-1}$  to  $R_0$  to 0.

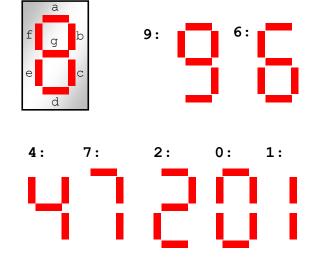

#### CODE CONVERTERS

#### **BCD TO 7-SEGMENT DECODER**

- The BCD system is useful as it provides a convenient human-readable format. For example, a keypad usually produces 4-bit BCD codes every time a user presses a key. A big challenge is to convert a series of 4-bit BCD codes into its binary representation. For example: 0101 1001 0111 = 597 in BCD, but 597 is 1001010101 in binary (unsigned).

- The BCD to 7-segment converter is a decoder because the number of outputs is greater than the number of inputs

- The truth table below assumes that the input and output are high-level.

| $\mathbf{b}_3$ | $b_2$ | $b_1$ | $\mathbf{b}_0$ | a | b | С | d | е | f | g |

|----------------|-------|-------|----------------|---|---|---|---|---|---|---|

| 0              | 0     | 0     | 0              | 1 | 1 | 1 | 1 | 1 | 1 | 0 |

| 0              | 0     | 0     | 1              | 0 | 1 | 1 | 0 | 0 | 0 | 0 |

| 0              | 0     | 1     | 0              | 1 | 1 | 0 | 0 | 1 | 0 | 1 |

| 0              | 0     | 1     | 1              | 1 | 1 | 1 | 1 | 0 | 0 | 1 |

| 0              | 1     | 0     | 0              | 0 | 1 | 1 | 0 | 0 | 1 | 1 |

| 0              | 1     | 0     | 1              | 1 | 0 | 1 | 1 | 0 | 1 | 1 |

| 0              | 1     | 1     | 0              | 1 | 0 | 1 | 1 | 1 | 1 | 1 |

| 0              | 1     | 1     | 1              | 1 | 1 | 1 | 0 | 0 | 0 | 0 |

| 1              | 0     | 0     | 0              | 1 | 1 | 1 | 1 | 1 | 1 | 1 |

| 1              | 0     | 0     | 1              | 1 | 1 | 1 | 1 | 0 | 1 | 1 |

| 1              | 0     | 1     | 0              | х | х | х | х | х | х | х |

| 1              | 0     | 1     | 1              | х | х | х | х | х | х | Х |

| 1              | 1     | 0     | 0              | х | х | х | х | х | х | х |

| 1              | 1     | 0     | 1              | х | х | х | х | х | х | Х |

| 1              | 1     | 1     | 0              | х | х | х | х | х | х | х |

| 1              | 1     | 1     | 1              | х | х | х | х | х | х | Х |

|                |       |       |                |   |   |   |   |   |   |   |

н

#### **GRAY TO BCD DECODER**

- It is a decoder because the number of outputs is equal to the number of inputs.

- The figure shows the truth table for a 4-bit case.

| $g_3 g_2 g_1 g_0$ | $b_{3}b_{2}b_{1}b_{0}$ |

|-------------------|------------------------|

| 0 0 0 0           | 0 0 0 0                |

| 0001              | 0001                   |

| 0011              | 0010                   |

| 0010              | 0011                   |

| 0 1 1 0           | 0100                   |

| 0 1 1 1           | 0101                   |

| 0 1 0 1           | 0110                   |

| 0100              | 0111                   |

| 1 1 0 0           | 1000                   |

| 1 1 0 1           | 1001                   |

| 1 1 1 1           | хххх                   |

| 1 1 1 0           | хххх                   |

| 1010              | хххх                   |

| 1011              | хххх                   |

| 1001              | хххх                   |

| 1000              | хххх                   |

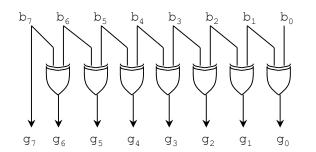

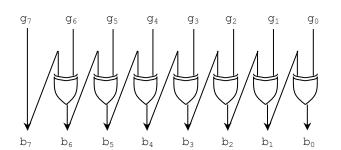

#### BINARY TO GRAY DECODER AND GRAY TO BINARY DECODER

- These are decoders because the number of outputs is equal to the number of inputs

- For small input sizes, we can use the truth table method (see Lecture Notes Unit 4). For large input sizes, the following circuits are way more efficient:

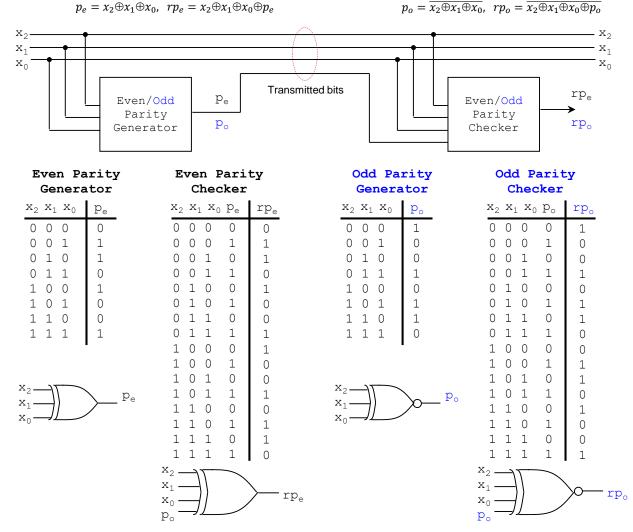

#### PARITY GENERATORS AND PARITY CHECKERS

- This is defined in the context of an error detection system with transmission and reception units.

- Data to be transmitted:  $X = x_{n-1}x_{n-2} \dots x_1x_0$  Transmitted stream:  $Y = x_{n-1}x_{n-2} \dots x_1x_0p$ , p: parity bit

- Parity definition:

- $\checkmark~$  Even Parity: Y has an even number of 1s  $\rightarrow$  pe=1, 0 otherwise

- ✓ Odd Parity: *Y* has an odd number of  $1s \rightarrow p_0=1$ , 0 otherwise.

- This definition is problematic since p is not known. An alternative definition, based on the actual data X is:

- ✓ Even Parity: X has an odd number of  $1s \rightarrow p_e = 1$ , 0 otherwise

- ✓ Odd Parity: X has an even number of  $1s \rightarrow p_0 = 1$ , 0 otherwise.

- Parity Generator: Circuit that generates the parity bit based on the actual data X

- **Parity Checker:** Circuit that verifies whether the stream Y has the correct parity.

#### Example:

- For the following error detection system,  $X = x_2 x_1 x_0$ , n = 3. The parity generator and checker are always of the same parity:

- $\checkmark$  Even Parity Generator: It generates the parity bit  $p_e$ .

- $\checkmark$  Odd Parity Generator: It generates the parity bit  $p_0$ .

- Even Parity Checker: It verifies that the received stream Y has even parity. If so,  $rp_e = 0$ , otherwise  $rp_e=1$  (to signal an error)

- ✓ Odd Parity Checker: It verifies that the received stream Y has odd parity. If so,  $rp_0=0$ , otherwise  $rp_0=1$  (to signal an error)

- In general for  $X = x_{n-1}x_{n-2} \dots x_1 x_0$ :  $p_e = x_{n-1} \oplus x_{n-2} \dots x_1 \oplus x_0$ .  $p_o = \overline{x_{n-1} \oplus x_{n-2} \dots x_1 \oplus x_0}$

- $\checkmark$  If the # of 1's in an n-bit stream is odd, the n-bit input XOR gate will return 1, 0 otherwise.

- ✓ If the # of 1's in an n-bit stream is even, the n-bit input XNOR gate will return 1, 0 otherwise.

- $rp_e = x_{n-1} \oplus x_{n-2} \dots x_1 \oplus x_0 \oplus p_e$ . We expect the number of 1s in Y to be even,  $\rightarrow$  an XNOR will detect this. However, we want  $rp_e$  to be 1 when this does not happen (to signal an error). Hence, we use an n + 1-bit input XOR gate.

- $rp_o = \overline{x_{n-1} \oplus x_{n-2} \dots x_1 \oplus x_0 \oplus p_o}$ . We expect the number of 1s in to be odd,  $\rightarrow$  an XOR will detect this. However, we want  $rp_o$  to be 1 when this does not happen (to signal an error). Hence, we use an n + 1-bit input XNOR gate.

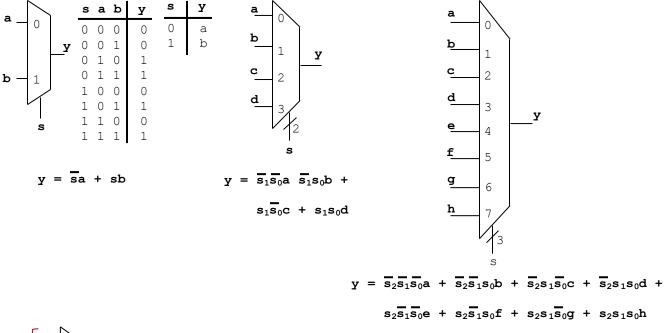

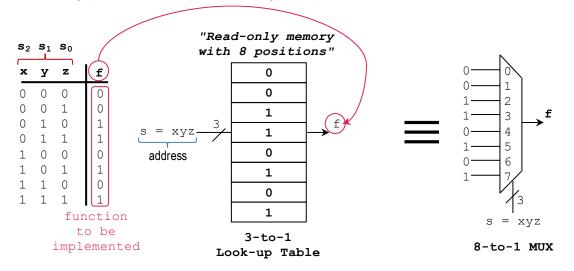

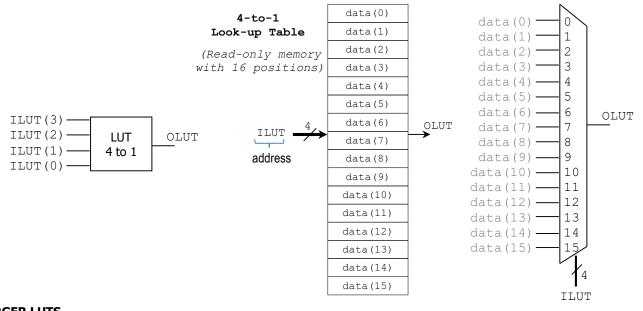

### LOOK-UP TABLES (LUTS)

- The LUT contents are hardwired in this circuit. A 4-to-1 LUT can be seen as a ROM with 16 addresses, each address holding

one bit. It can also be seen as a multiplexor with fixed inputs.

- This is how FPGAs implement logic functions. A 4-to-1 LUT can implement any 4-input logic function.

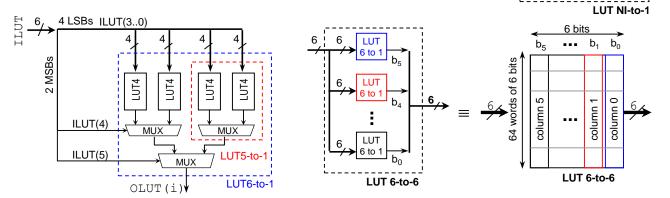

#### LARGER LUTS

- A larger LUT can be generated by building a circuit that allows for more ROM positions.

- Efficient method: A larger LUT can also be built by combining LUTs with multiplexers as shown in the figure on the right. We can build a NI-to-1 LUT with this method.

- The figure below shows a case for a LUT 6-to-1 built out of two LUT 5-to-1. Each LUT 5to-1 is built out of two LUT 4-to-1.

- We can build a NI-to-NO LUT using NO NI-to-1 LUTs. This can be seen as a ROM with 2<sup>NI</sup> addresses, each address holding NO bits.

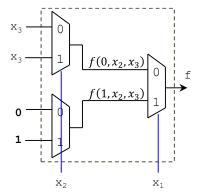

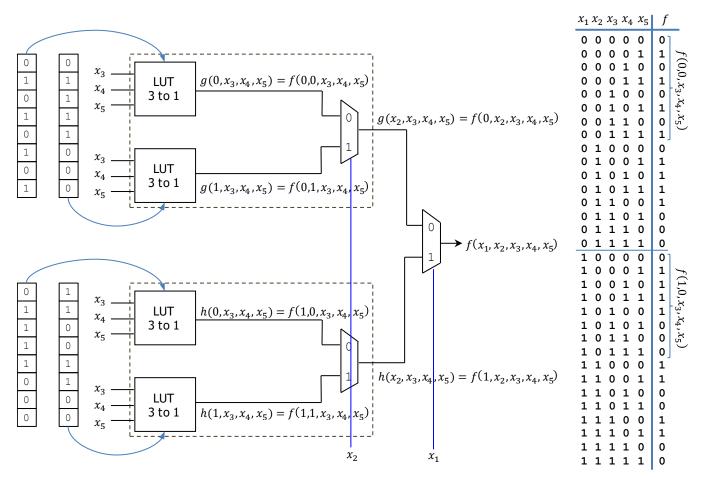

#### LUT DECOMPOSITION USING SHANNON EXPANSION

• LUT size grows exponentially with the size of the input. For a *n*-variable Boolean function, Shannon expansion provides a systematic way of implementing that function with LUTs and multiplexors, thereby optimizing resources.

NI

NI-1

LUT

NI1 to 1

LUT

NI1 to 1

#### Example:

• Using 3-to-1 LUTs and 2-to-1 MUXes, implement the following Boolean function (specify the contents of the LUTs):  $f(x_1, x_2, x_3, x_4, x_5) = x_1 x_2 \overline{x_4} + x_3 \oplus (x_4 + x_5) + \overline{x_1} \overline{x_2} x_5$

#### \*\*\*\*\*

$$f = \overline{x_1} f(0, x_2, x_3, x_4, x_5) + x_1 f(1, x_2, x_3, x_4, x_5) = \overline{x_1} (x_3 \oplus (x_4 + x_5) + x_2 \overline{x_5}) + x_1 (x_2 \overline{x_4} + x_3 \oplus (x_4 + x_5))$$

$\checkmark \quad g(x_2, x_3, x_4, x_5) = f(0, x_2, x_3, x_4, x_5) = x_3 \oplus (x_4 + x_5) + \overline{x_2} x_5$

$$g = \overline{x_2}g(0, x_3, x_4, x_5) + x_2g(1, x_3, x_4, x_5) = \overline{x_2}(x_3 \oplus (x_4 + x_5) + x_5) + x_2(x_3 \oplus (x_4 + x_5))$$

Note that:  $g(0, x_3, x_4, x_5) = f(0, 0, x_3, x_4, x_5)$ ,  $g(1, x_3, x_4, x_5) = f(0, 1, x_3, x_4, x_5)$

✓

$$h(x_2, x_3, x_4, x_5) = f(1, x_2, x_3, x_4, x_5) = x_2 \overline{x_4} + x_3 \oplus (x_4 + x_5)$$

$$h = \overline{x_2}h(0, x_3, x_4, x_5) + x_2h(1, x_3, x_4, x_5) = \overline{x_2}(x_3 \oplus (x_4 + x_5)) + x_2(\overline{x_4} + x_3 \oplus (x_4 + x_5))$$

Note that:  $h(0, x_3, x_4, x_5) = f(1, 0, x_3, x_4, x_5), h(1, x_3, x_4, x_5) = f(1, 1, x_3, x_4, x_5)$

These four 3-variable functions will be implemented using 3-to-1 LUTs. We are ready to sketch the circuit using 3-to-1 LUTs and 2-to-1 MUXes. This is how multi-variable functions are implemented on FPGAs.

In order to get the LUT contents, we can either evaluate every 3-variable function that was generated, or we can just fill up the truth table for f and identify the LUT contents for each 3-variable function.

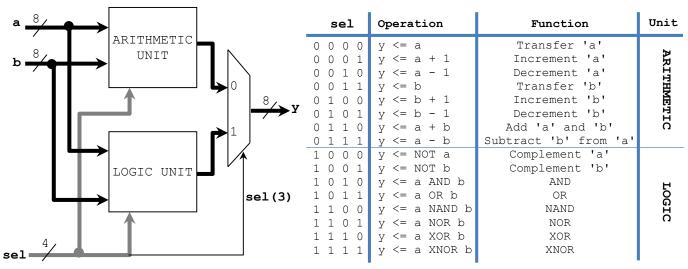

#### ARITHMETIC LOGIC UNIT (ALU)

Two types of operation: Arithmetic and Logic (bit-wise). The sel(3..0) input selects the operation. sel(2..0) selects the operation type within a specific unit. The arithmetic unit consist of adders and subtractors, while the Logic Unit consist of 8-input logic gates.

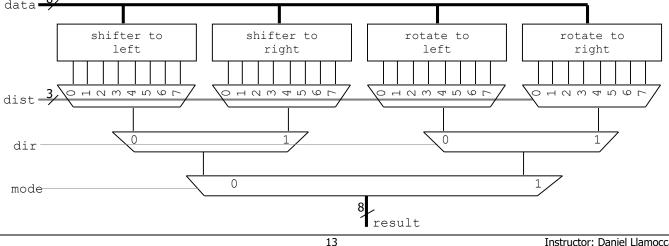

#### BARREL SHIFTER

- Two types of operation: Arithmetic (mode=0,  $\times 2^{i}$ ) and Rotation (mode=1)

- Truth table for an 8-bit Barrel Shifter:

result[7..0] (output): It is shifted version of the input data[7..0]. sel[2..0]: number of bits to shift. dir: It controls the shifting direction (dir=1: to the right, dir=0: to the left). When shifting to the right in the Arithmetic Mode, we use sign extension so as properly account for signed input numbers.

|      | mode = 0. | ARITHMETIC M | ODE        | mode = 1. ROTATION MODE |          |          |            |  |  |  |

|------|-----------|--------------|------------|-------------------------|----------|----------|------------|--|--|--|

| dir  | dist[20]  | data[70]     | result[70] | dir                     | dist[20] | data[70] | result[70] |  |  |  |

| Х    | 0 0 0     | abcdefgh     | abcdefgh   | Х                       | 0 0 0    | abcdefgh | abcdefgh   |  |  |  |

| 0    | 001       | abcdefgh     | bcdefgh0   | 0                       | 001      | abcdefgh | bcdefgha   |  |  |  |

| 0    | 0 1 0     | abcdefgh     | cdefgh00   | 0                       | 0 1 0    | abcdefgh | cdefghab   |  |  |  |

| 0    | 0 1 1     | abcdefgh     | defgh000   | 0                       | 0 1 1    | abcdefgh | defghabc   |  |  |  |

| 0    | 1 0 0     | abcdefgh     | efgh0000   | 0                       | 100      | abcdefgh | efghabcd   |  |  |  |

| 0    | 1 0 1     | abcdefgh     | fgh00000   | 0                       | 101      | abcdefgh | fghabcde   |  |  |  |

| 0    | 1 1 0     | abcdefgh     | gh000000   | 0                       | 1 1 0    | abcdefgh | ghabcdef   |  |  |  |

| 0    | 1 1 1     | abcdefgh     | h0000000   | 0                       | 1 1 1    | abcdefgh | habcdefg   |  |  |  |

| 1    | 001       | abcdefgh     | aabcdefg   | 1                       | 001      | abcdefgh | habcdefg   |  |  |  |

| 1    | 0 1 0     | abcdefgh     | aaabcdef   | 1                       | 0 1 0    | abcdefgh | ghabcdef   |  |  |  |

| 1    | 0 1 1     | abcdefgh     | aaaabcde   | 1                       | 0 1 1    | abcdefgh | fghabcde   |  |  |  |

| 1    | 1 0 0     | abcdefgh     | aaaaabcd   | 1                       | 100      | abcdefgh | efghabcd   |  |  |  |

| 1    | 1 0 1     | abcdefgh     | aaaaabc    | 1                       | 101      | abcdefgh | defghabc   |  |  |  |

| 1    | 1 1 0     | abcdefgh     | aaaaaab    | 1                       | 1 1 0    | abcdefgh | cdefghab   |  |  |  |

| 1    | 1 1 1     | abcdefgh     | aaaaaaaa   | 1                       | 1 1 1    | abcdefgh | bcdefgha   |  |  |  |

| data | 8,        | ·            |            |                         | 1        | -        |            |  |  |  |

## PRACTICE EXERCISES

1. Implement the following functions using i) decoders and ii) multiplexers:

| $\checkmark$ $F = \overline{X + Y} + ZY$     | $\checkmark  F = (X + Y + Z)(X + Y + \overline{Z})$ |

|----------------------------------------------|-----------------------------------------------------|

| $\checkmark$ $F(X,Y,Z) = \sum (m_0,m_2,m_6)$ | $\checkmark$ F = XY + YZ + XZ                       |

| $\checkmark  F(X,Y,Z) = \prod(M_2,M_4,M_7)$  | $\checkmark  F = X \oplus Y \oplus Z$               |

- 2. Using ONLY 4-to-1 MUXs, implement an 8-to-1 MUX.

- 3. Implement a 6-to-1 MUX using i) only NAND gates, and ii) only NOR gates.

- 4. Verify that the following circuit made of out of five 2-to-4 decoders with enable represents a 4-to-16 decoder with enable. Tip: Create the truth table.

- 5. Using only 2-to-1 MUXs, implement the XOR and XNOR gates.

- 6. Using only a 4-to-1 MUX, implement the following functions.

- $F(X,Y,Z) = \sum (m_1, m_3, m_5, m_7).$

$$F(X, Y, Z) = \sum (m_1, m_3, m_5)$$

- $F(X, Y, Z) = \sum (m_3, m_5, m_7).$

- $F(X,Y,Z) = \sum (m_5,m_7).$

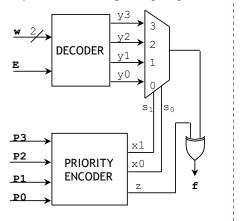

7. Complete the following timing diagram: